SEV-SNP - 3rd generation Secure Encrypted Virtualization - Secure Nested Paging.CLRSSBSY, INCSSP, RDSSP, RSTORSSP, SAVEPREVSSP, SETSSBSY, WRSS, WRUSS.CET_SS - Control-flow Enforcement Technology / Shadow Stack.TLBSYNC - Synchronize TLB invalidations.INVLPGB - Invalidate TLB entry(s) with broadcast to all processors.INVPCID - Invalidate TLB entry(s) in a specified PCID.VPCLMULQDQ - 256-bit Vector Carry-Less Multiplication of Quadwords.VAESENCLAST - AES Last Encryption Round.VAESDECLAST - AES Last Decryption Round.Zen 3 introduced the following ISA enhancements: This list is incomplete you can help by expanding it. Page table walkers tripled from 2 to 6 for TLB miss handling.Store queue increase from 48 to 64 slots.Store throughput increased from 1 to 2, if not 256b.

Load throughput increased from 2 to 3, if not 256b.(Unsigned operations are ~1 cycle faster for some of both old/new cases.) Throughput improves proportionately. Instruction redundancy increased between ports for reduced bottlenecking on a wider variety of instruction streams.Schedulers shared between pairs of ALU + AGU/branch ports instead of dedicated for each.Issue increased from 7 (existing 4 ALU and 3 AGU) to 10 with 1 new dedicated branch execution port and 2 separated store data pathways.Integer physical register file increased from 180 to 192 entries.Hardware implementation of BMI2 PDEP/PEXT bit scatter/gather operations, compared to prior microcode emulation.256b VAES and VPCLMULDQ support for doubled AES and AES-GCM cryptographic throughput.Unified scheduler split into 1 scheduler per FMA/FADD/transfer port set.Fifth and sixth dedicated execution ports added for floating point store and FP-to-int transfer, no longer sharing 2nd FADD port.FMA latency reduced by 1 cycle from 5 to 4.L1 BTB doubled from 512 to 1024 entries.

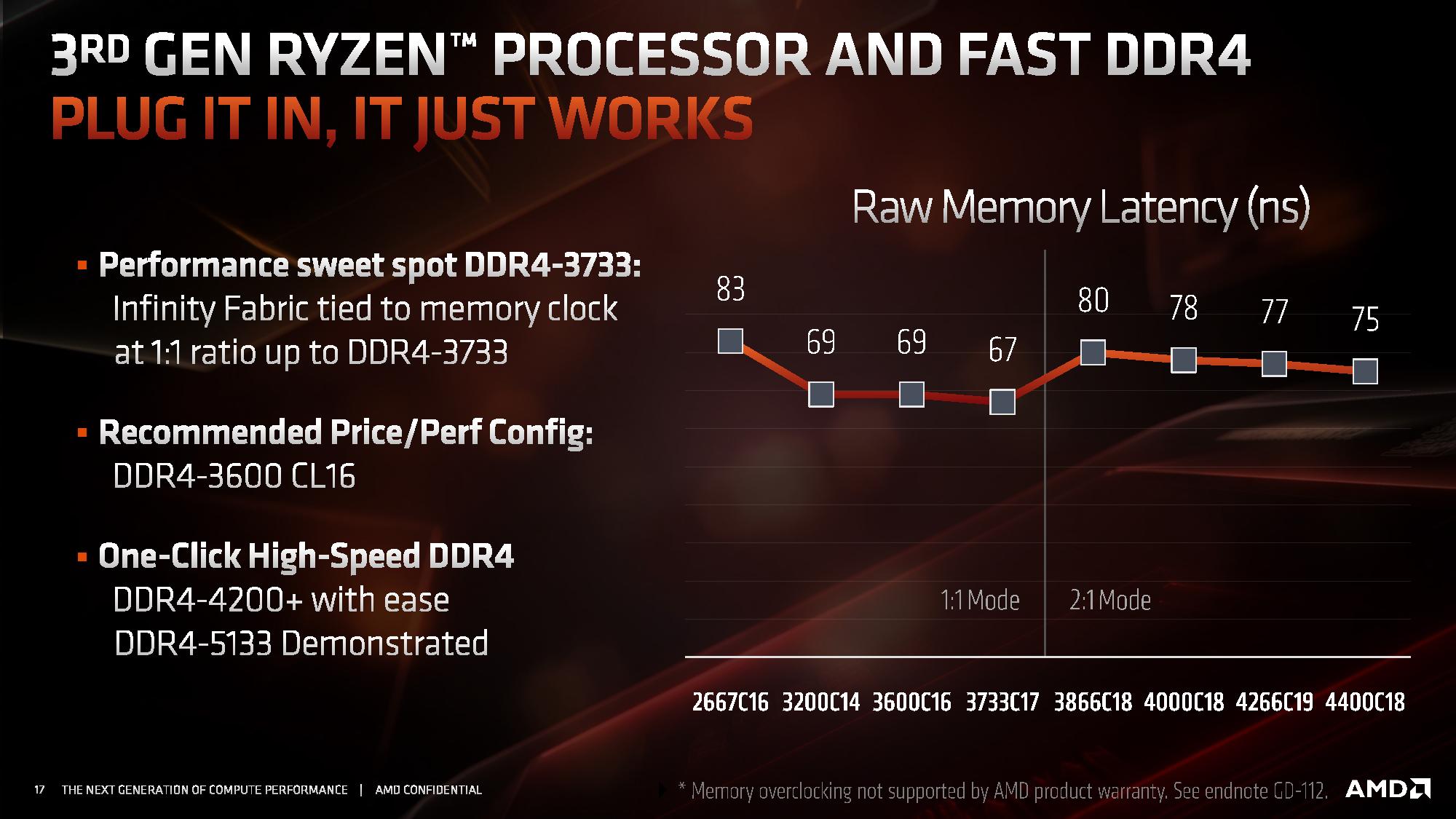

WHICH RAM FOR ZEN 3 SERIES

Note: Only the APU series of microprocessors retains the monolithic design, so they are fabricated solely on TSMC's 7nm+ process. Zen 3 is fabricated on TSMC's 7nm+ process for the Core Compute Die (CCD), the same process used in Zen 2 Refresh processors, as well as GlobalFoundries 12nm process for the Input/Output Die (IOD). Mainstream desktop & mobile processors with integrated GPU Mainstream to high-end desktops & enthusiasts market processors Information may be incomplete and can change by final release. Preliminary Data! Information presented in this article deal with future products, data, features, and specifications that have yet to be finalized, announced, or released.

0 kommentar(er)

0 kommentar(er)